標簽:LM12H458(1)信號處理(217)MCU(950)

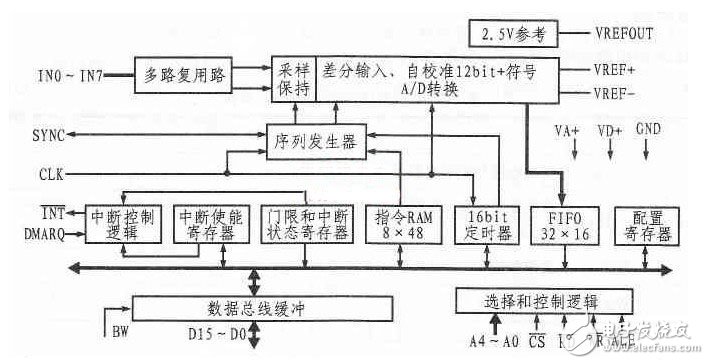

LM12H458($15.4125)是高集成度的數據采集系統DAS芯片,它將采樣保持、A/D轉換集成在一塊芯片內,從而大大減少了外圍電路的設計。其8路模擬信號輸入既可作為單端輸入,又可兩兩組成差分輸入。器件內部提供的一個2.5V參考電壓、8×48bit指令RAM和32×16bit的FIFO大大減小了微處理器的負擔。LM12H458的工作電壓為3~5.5V,功耗小于34mW,待命模式下的功耗只有50μW。此外,LM12H458還有如下主要性能:

有三種工作模式:分別為帶符號的13位模式、帶符號的9位模式和看門狗模式;有8個模擬信號輸入通道,模擬信號可單端輸入,也可差分輸入;內置采樣保持和2.5V參考電壓;內含32×16bit的FIFO;采樣時間和轉換速率可編程;具有自校準和診斷模式;帶有8位或16位數據總線。

圖1LM12H458內部功能框圖

引腳功能和功能說明

LM12H458的引腳功能如表1所列。圖1為其內部功能框圖。LM12H458是一個多功能數據采集系統,其內部的電荷重分配ADC采用電容梯形網絡代替普通的電阻梯形網絡,并使用逐步逼近寄存器的DAC使VREF-和VREF+之間產生一個中間電壓,該電壓與輸入的采樣電壓相比較可產生數字輸出的每一位,中間電壓的個數和比較的次數對應于ADC的分辨率,通過校準ADC中的電容網絡可校準數字輸出的每一位精度。LM12H458有兩種不電感廠家同的校準模式:一種是補償偏移電壓或零誤差,在該模式下只測量一次偏移誤差,并依此建立修正系數;另一種為修正偏移誤差和ADC線性誤差,稱為全校準。將該模式下的偏移誤差測量八次,并取平均值即可建立修正系數。上述兩種模式的修正系數被存貯在內部的偏移修正寄存器中。LM12H458的線性修正是通過修正內部DAC的失配電容獲得的,在LM12H458內部ROM中存有校準算法,可對每一個電容校準8次并取平均值,從而產生線性修正系數。一旦校準后,內部算術邏輯單元(ALU)即可使用偏移誤差修正系數和線性修正系數來修正每一次的轉換結果。看門狗模式用于監控單端輸入或差分輸入信號的幅值。每個采樣信號都有上下兩個門限,輸入信號高于或低于某一門限值都會產生中斷。

表1 LM12H458的腳符號及功能

LM12H458是一個多功能數據采集系統,內部有28個16bit的寄存器,各個寄存器的功能如下:

配置寄存器是DAS的控制中心,可用于控制序列器的啟動和停止、復位RAM指針和標志、設置待命狀態、校準偏移和線性誤差、選擇RAM區等。指令RAM分為三個區:指令區、門限1區、門限2區。每一條指令(48bit=3X16bit)分散在三個16比特字寬的RAM區中,三個區的選擇可由配置寄存器2bit的RAM指針來控制。指令區可設置通道的選擇、工作模式、采樣時間和循環位。其它兩個區用于設置上下門限值。DAS可從指令0連續執行所有設置的指令,執行的最后一條指令的循環位為1時,再返回到指令0。指令執行期間,微處理器不能訪問指令RAM,只有處理器終止指令循環后才可訪問。FIFO為只讀寄存器,可用于存儲轉換結果。中斷使能寄存器可使用戶激活8個中斷源,該寄存器的高字節與中斷1、2有關。

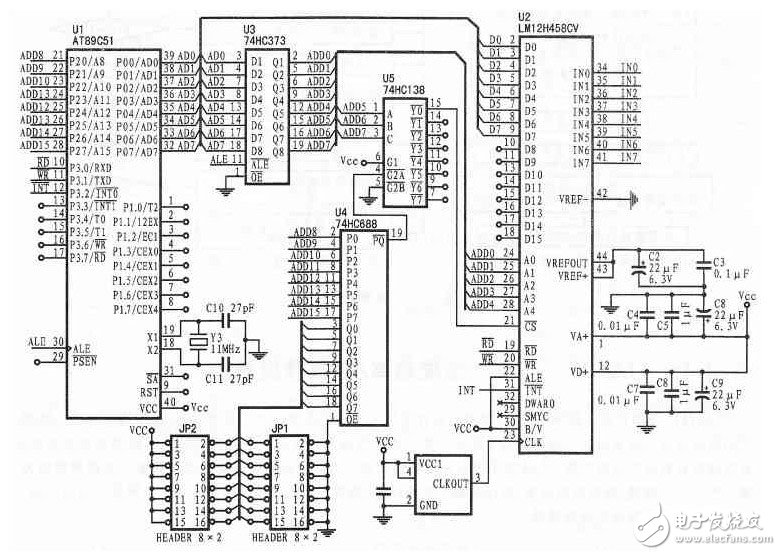

圖2 LM12H458與80C51的接口電路

中斷狀態寄存器和門限狀態寄存器用于指示DAS中斷源和輸入信號是否超過上門限或下門限。定時寄存器用于設置指令執行前的等待時間。而指令寄存器的bit9可使能或禁止插入等待時間。LM12H458有8個中斷源,各中斷具有同等的優先級別,中斷使能寄存器可使能或禁止相應的中斷,當發生中斷時,中斷狀態寄存器相應的位置1。各個中斷對應的功能如下:

硬件電路設計

LM12H458靈活的總線接口簡化了與多種微處理器的接口,它既可與8位處理器相連,又可方便地與16位微處理器相連。圖2為 AT89C51($3.7500)與DAS的接口電路圖。該電路采用全地址譯碼方式來產生DAS的片選信號CS,其DAS映射的地址空間為0000-001F,數據總線寬度為8bit。圖中的74HC373($0.1082)用于鎖存低8位地址,而 大功率電感廠家 |大電流電感工廠