序論

許多比較老的線性器件,尤其是運算放大器,簡稱“運放”,都沒有SPICE宏模型。即使有,通常使用的也是博伊爾(Boyle)宏模型,該模型以今天的標準來看準確度并不高,即使提供給用戶也不能很好地代表實際器件。

這種基于晶體管的方法使用相對簡單的方程式 —— 工程師可對這些方程式進行相應的修改,以滿足各種放大器設計流程的需要。我們的理念是用來自產品說明書的幾個參數來創建SPICE(TINA-TI™)宏模型,不管輸入或輸出拓撲結構如何。該技術基于這樣的假設:大多數運算放大器都有一個遠遠超出單位增益帶寬的次極。

一般而言,工程師需要以下參數:電源電壓、開環增益與負載、單位增益帶寬、壓擺率、輸入共模范圍、共模抑制比(CMRR)、電源抑制比(PSRR)、Vos、Ios、Ib、開環輸出阻抗、相位裕度、寬帶噪聲與1/f噪聲、電源電流以及短路電流。對于軌至軌輸出,工程師將需要輸出飽和電壓(輸入輸出電壓差)以及匯點和源點電流。此外,還需要明確規定負載電阻RL。

以不同顏色突出顯示的方程式是工程師需插入到網表中的方程式。藍色方程式是為了方便工程師自己進行觀察;紅色方程式則是網表末尾的模型參數中可能需要的。

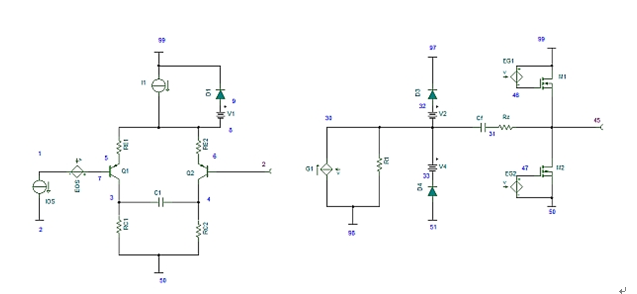

圖1展示了雙極性輸入和互補金屬氧化物半導體(CMOS)輸出級的拓撲結構。

圖1:非軌至軌雙極性輸入和CMOS輸出運放的三級拓撲結構

輸入級

輸入級包括:一個差分對(Q1/Q2);電流I1、D1和V1 —— 它們可將共模設置為高電平;Rc1和Rc2;可設置次極的C1;作為發射極負反饋的RE1和RE2;EOS —— 一個非反相輸入串聯的壓控電壓源。該電壓源有好幾個組成部分。第一個代表輸入偏移電壓;第二個與共模抑制比(CMRR)有關聯;第三個與電源抑制比(PSRR)有關聯,等等。 大功率電感廠家 |大電流電感工廠