引言

許多現代數據采集系統均是由高速和高精度ADC組成的。由于其低成本和低功模壓電感耗,基于CMOS開關型電容器的ADC通常被用于此類設計中。ADC使用一個無緩沖前端,直接耦合至采樣網絡。為了有效地最小化噪聲和信號失真,需使用一款高速、低噪聲和低失真的運算放大器來驅動該ADC。為了使失真最小化,將運算放大器輸出在ADC采集時間內調節到理想的精度是非常重要的。通常,運算放大器建立時間是根據產品說明書中規定的頻率響應時間計算得出的,也可以通過具有精度限制功能的示波器對輸出進行測量得出,有時需要將運算放大器的輸入與輸出差值放大來實現更高的精度。但這些方法均受示波器精度以及電路寄生的限制。此外,運算放大器的建立時間還受由示波器探針導入的寄生電容和電感的影響。第二種方法是將運算放大器的輸入輸出差值放大來提高測量的精度。以上這些方法均未考慮 ADC 采樣電路和采樣數據包中的寄生電容和電感。

建立時間的定義

建立時間是指從理想的瞬時步進應用輸入到閉環放大器的輸出達到并保持在一個規定的對稱性誤差范圍的時間。建立時間包括一個非常短暫的傳播延遲時間,以及將輸出轉換至最終值近似值所需的時間,然后結合轉換從過載條件下恢復,最后穩定在規定誤差范圍內。對于高精度ADC來說,規定的誤差范圍通常為一個最低位(LSB)ADC的四分之一。

基本設置

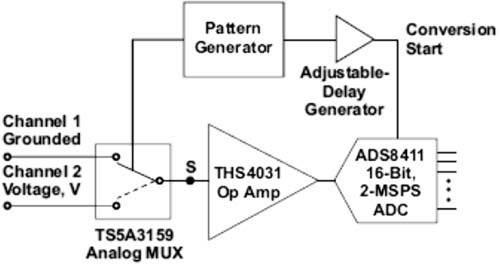

此處使用的 ADC 是 TI 推出的 ADS8411,該器件是一款 16 位 2-MSPS 的逐次逼近寄存器 (SAR) ADC。驅動器運算放大模壓電感器器為 TI THS4031。圖 1 顯示了評估設置。

圖 1 建立時間評估設置

利用一個模擬多路器 (MUX)(型號為 TI TS5A3159),通過開關其 2 個通道來產生瞬時步進輸入。直流電壓 V 連接到通道 2,通道 1 連接至接地;該設置可以產生一個步進輸入,從零電壓升至有電壓,或從有電壓降至零電壓。此外,可以通過步進發生器來產生步進輸入。步進發生器的建立時間速度要比運算放大器的建立時間快許多。

說明

步驟 1

ADC 首先對通道 1(連接至接地)進行采樣。需要有一個較電感器圖形符號長的采樣時間以確保 ADC 的輸入電容被完全放電。

步驟 2

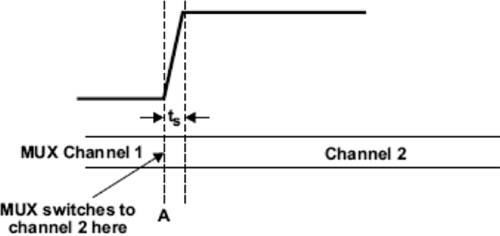

如圖 2 所示,在瞬時 A 時,將模擬 MUX 從通道 1 切換到通道 2。該圖顯示了將 MUX 從通道 1 切換到通道 2 時 S 點(圖 1)的電壓。MUX 的建立時間用 ts 標識出來。假設 ts 比運算放大器的建立時間要短。

圖 2 MUX 通道變化的建立時間

步驟3

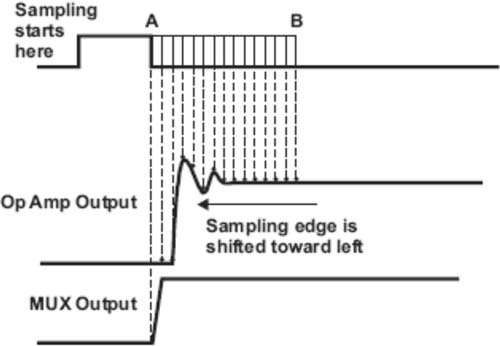

一旦在瞬時 A 點開啟模擬 MUX,運算放大器的輸入就會電感器生產立即開始發生變化。在瞬時 A 點之后,經過一個非常短暫的傳播延遲,運算放大器的輸出開始變化。通過轉換率和產品說明書中規定的帶寬可以大概計算出運算放大器建立時間 (tideal)。本文提出的方法描繪了運算放大器在瞬時 A 點到瞬時 B 點時的輸出(如圖 3)。瞬時 B 點和瞬時 A 點之間的差為 2tideal。

圖 3 對 A 點到 B 點的 N 個采樣求平均值,提高精確度

步驟 4

第一個 ADC 采樣點是在瞬時 B 點,并記錄下該點 n 個讀數值(ADC 的數字輸出)。求出這些數值的平均值,使其更為精確(稍后進行討論)。借助圖形發生器和可調時延發生器(見圖 1),向左移 1 個毫微秒單位,得出下一個采樣點(見圖 3),再記錄下該點的 n 個數值。按照此法,采樣點每次以 1 個毫微秒單位從瞬時 B 點逐步移向瞬時 A 點,并以陣列的方差模電感器式存儲每個采樣點平均值。該陣列是按照逆時間順序繪制出來的,從而得出運算放大器輸出建立時間的實圖(如圖 3 所示)。

求平均值,以獲得更高精度

N 位 ADC 的輸入應該最少設定為 n+2 位,但測量出的輸出在 ADC 上顯示為 n 位數字代碼。通過重復采樣同一個輸入和采用多個 (n) ADC 讀數值,可以提高精度。最后求出 n 個輸出數字代碼的平均值。這表明精度每增加一位,讀數值數量則為 4 個,因此精度增加了 w 位,則需要 4w 個讀數值。 大功率電感廠家 |大電流電感工廠